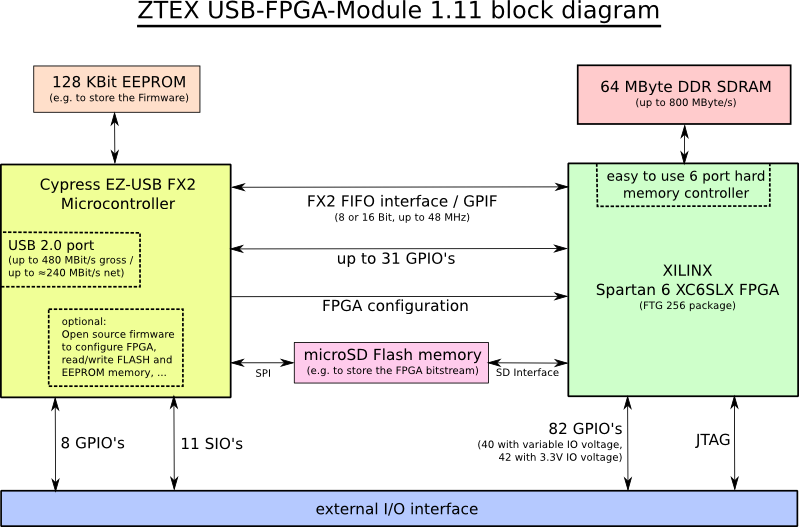

Spartan 6 Block Diagram

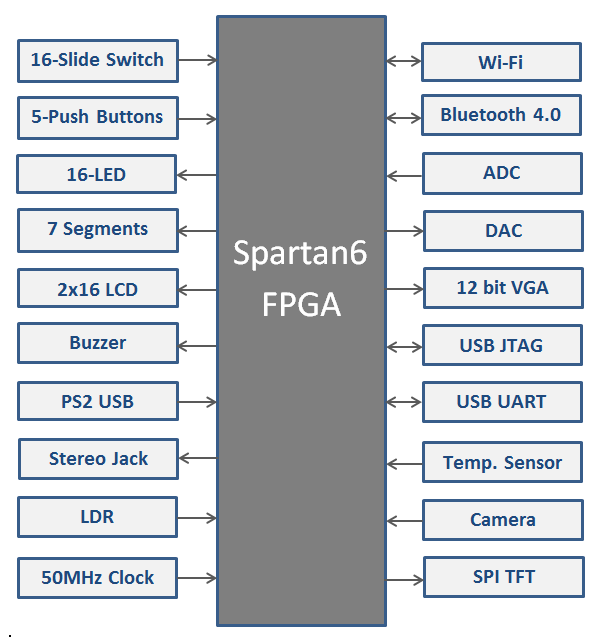

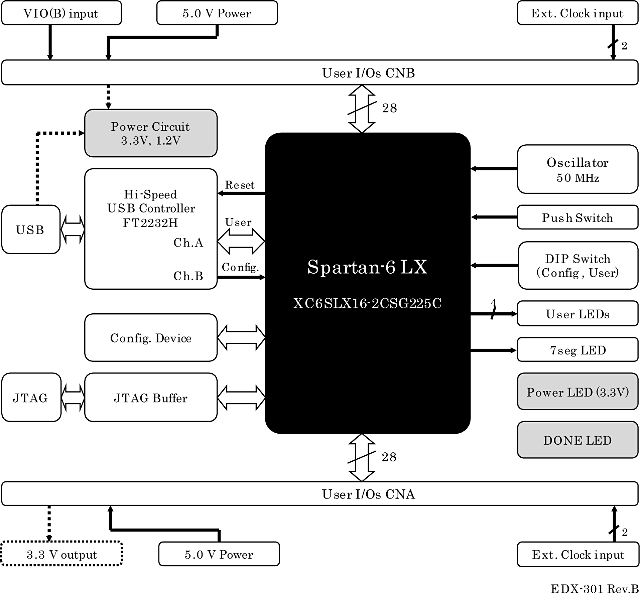

100 general purpose i o s gpio connected to fpga.

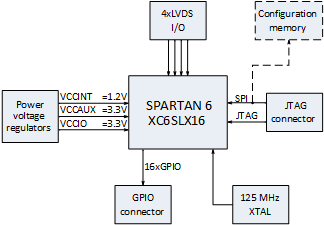

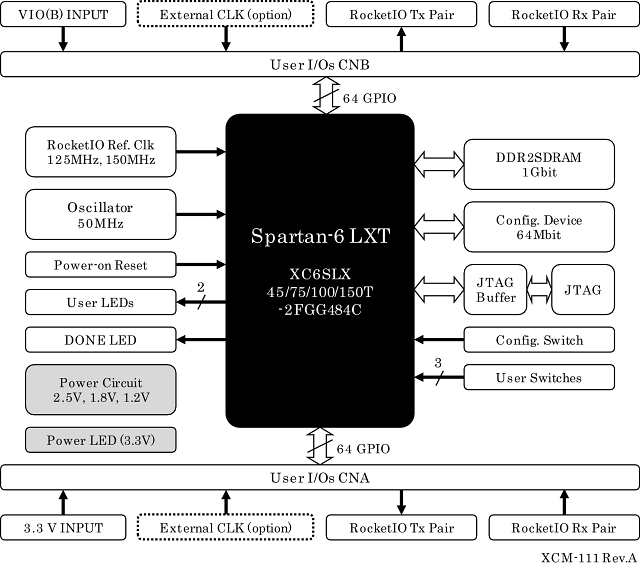

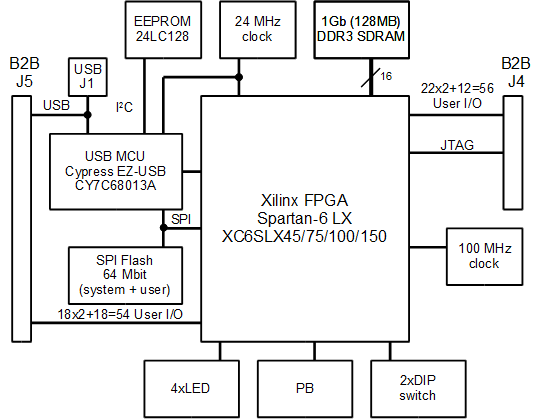

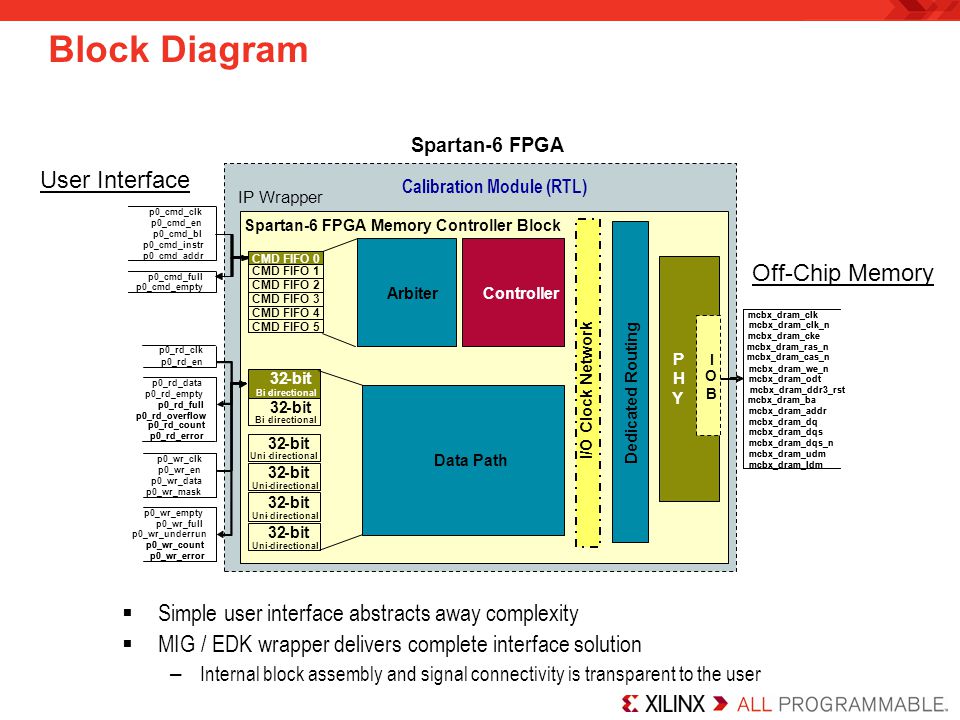

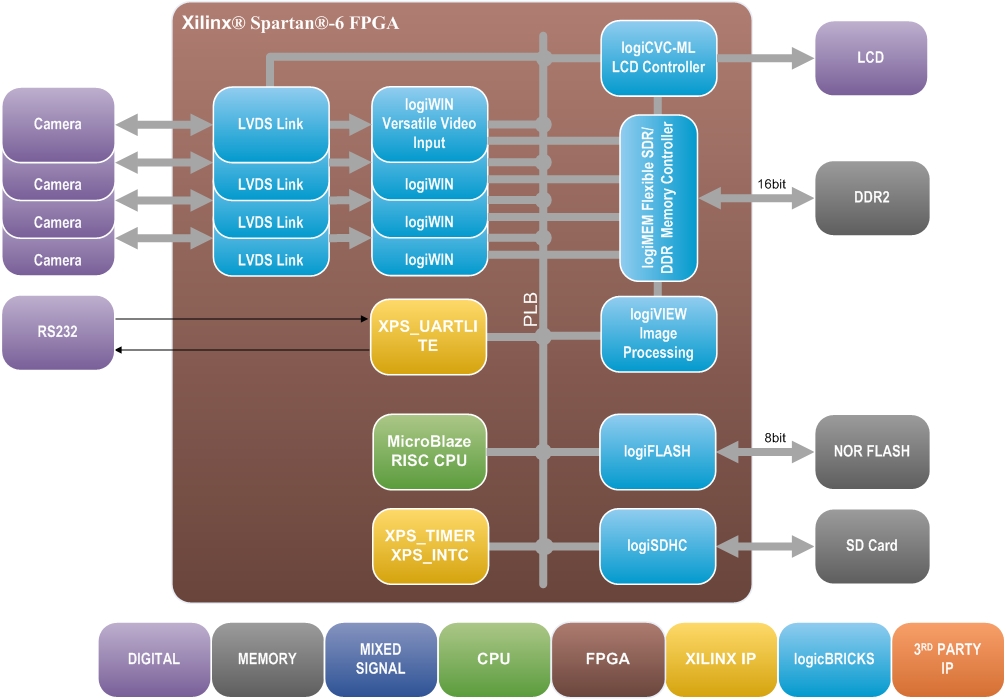

Spartan 6 block diagram. Aes s6mb lx9 g xilinx spartan 6 fpga lx9 microboard 89 usd featured manufacturers block diagram rj45 rj45 hdmi connector rgmii phy 8 dip switches pc4 header digilent usb jtag module usb uart 5 push switches 8 user leds ddr4 sdram x32 1gb 250 mhz differential system clock programmable gth clock source single qspi 32mb user code flash. Due to the transceivers the lx and lxt pinouts are not compatible. Spartan 6 devices offer industry leading connectivity features such as high logic to pin ratios small form factor packaging microblaze soft processor and a diverse number of supported i o protocols ideally suited for a range of advanced bridging. The table below highlights the typical max currents each power output of the tps650250 converters to the rails of the spartan 6 lxt.

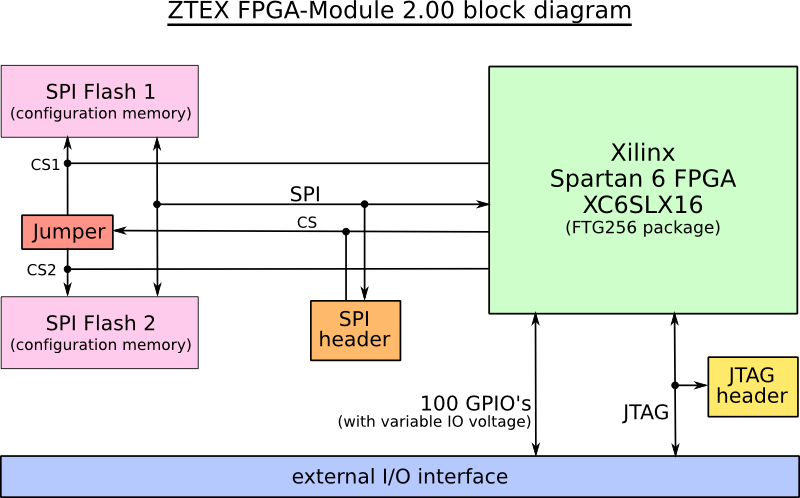

Shipments to at least 2027. Xilinx spartan 6 fpga lx150 xc6slx150 fpga speed grade 3 or 3n. High speed 480 mbit s usb interface via mini usb connector b type. External power 4 5 v.

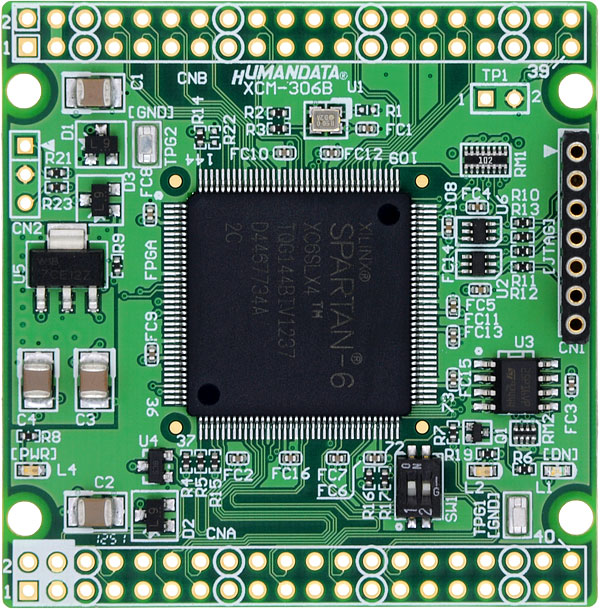

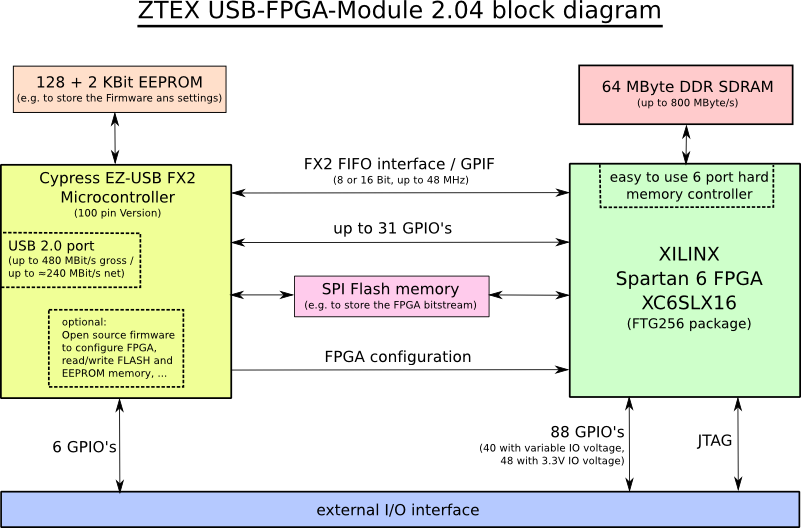

16 v input. Xilinx spartan 6 xc6slx16 fpga xc6slx9 and xc6slx25 on request external i o connector consisting in two female 2x32 pin headers with 2 54mm grid provides. Ise tools on windows 10.